标签:

在数字系统中,由于采用二进制运算处理数据,因此通常将信息变成若干位二进制代码。在逻辑电路中,信号都是以高,低电平的形式输出。编码器:实现编码的数字电路,把输入的每个高低电平信号编成一组对应的二进制代码。

设计一个输入为8个高电平有效信号,输出代码为原码输出的3位二进制编码器。

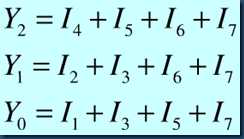

化简逻辑表达式: 由逻辑表达式可以得出,普通的8-3编码器用或门即可实现。对应的verilog程序如下:

由逻辑表达式可以得出,普通的8-3编码器用或门即可实现。对应的verilog程序如下:

module mb_83(x,y); input [7:0]x; output [2:0]y; reg [2:0]y; always@(x) begin case (x) 8‘b00000001:y=3‘b000; //当 当 x=8 ’b00000001,则 则 y 输出为 3 ’b000 8‘b00000010:y=3‘b001; //当 当 x=8 ’b00000010,则 则 y 输出为 3 ’b001 8‘b00000100:y=3‘b010; //当 当 x=8 ’b00000100,则 则 y 输出为 3 ’b010 8‘b00001000:y=3‘b011; //当 当 x=8 ’b00001000,则 则 y 输出为 3 ’b011 8‘b00010000:y=3‘b100; //当 当 x=8 ’b00010000,则 则 y 输出为 3 ’b100 8‘b00100000:y=3‘b101; //当 当 x=8 ’b00100000,则 则 y 输出为 3 ’b101 8‘b01000000:y=3‘b110; //当 当 x=8 ’b01000000,则 则 y 输出为 3 ’b110 8‘b10000000:y=3‘b111; //当 当 x=8 ’b10000000,则 则 y 输出为 3 ’b111 default: y=3‘b000; endcase end endmodule

上述编码器有一个缺点,即在某一个时刻只允许有一个有效的输入,而同时若又有两个或两个以上的输入信号要求编码,输出端一定会发生混乱,出现错误。为了解决这个问题,引入了优先编码器。优先编码器的功能是允许同时在几个输入端有输入信号,编码器按照输入信号预先排定的优先顺序,只对同时输入的几个信号中有优先权高位的一个信号编码。

对应的真值表为

对应的verilog程序:(输入信号:i[7:0];输入使能端:ei;输出信号端:y: [2:0];输出使能端eo;优先标志端gs)

module yxbm_83(y,eo,gs,i,ei); input [7:0] i; //8 位输入 i input ei; // 使能输入端 ei output eo,gs; // 使能输出端 eo ,优先标志端 gs output[2:0] y; //3 位输出 y reg[2:0] y; //3 位输出寄存器 y reg eo,gs; // 使能输出寄存器, always@(i,ei) // 电平触发方式,当 i 跟 跟 ei 有改变的时候,执行以下操作 begin if(ei==1‘b1) //当 ei 为 为 1 的时候 begin y<=3‘b111; gs<=1‘b1; eo<=1‘b1; end else begin if(i[7]==1‘b0) //当 i 的第 8 为 为 0 时候 begin y<=3‘b000; gs<=1‘b0; eo<=1‘b1; end else if(i[6]==1‘b0) //当 i 的第七位为 0 时候 begin y<=3‘b001; gs<=1‘b0; eo<=1‘b1; end else if(i[5]==1‘b0) //当 i 的第 6 位为 0 时候 begin y<=3‘b010; gs<=1‘b0; eo<=1‘b1; end else if(i[4]==1‘b0) //当 i 的第 5 位为 0 时候 begin y<=3‘b011; gs<=1‘b0; eo<=1‘b1; end else if(i[3]==1‘b0) //当 i 的第 4 位为 0 时候 begin y<=3‘b100; gs<=1‘b0; eo<=1‘b1; end else if(i[2]==1‘b0) //当 i 的第 3 位为 0 时候 begin y<=3‘b101; gs<=1‘b0; eo<=1‘b1; end else if(i[1]==1‘b0) //当 i 的第 2 位为 0 时候 begin y<=3‘b110; gs<=1‘b0; eo<=1‘b1; end else if(i[0]==1‘b0)//当 i 的第 1 位为 0 时候 begin y<=3‘b111; gs<=1‘b0; eo<=1‘b1; end else if(i==8‘b11111111)//当 i 为 为 8‘b11111111 时候 begin y<=3‘b111; gs<=1‘b1; eo<=1‘b0; end end end endmodule

时序仿真的结果:

译码器(Decoder):把代码状态的特定含义翻译过来的过程为译码。译码器:实现译码操作的逻辑电路,就是把一种代码转换为另一种代码的电路。

译码器与编码器图解:

设计一个具有三个使能端的3-8译码器:

真值表为:3位编码输入端a[2:0],使能输入端g1,g2,g3;输出信号:8位编码输出端y[7:0]。

module ym_3_8(a,g1,g2,g3,y); input[2:0] a; //3 位 位 2 进制编码输入端 input g1,g2,g3; //3 个使能输入端 output[7:0] y; //8 位编码输出端 reg[7:0] y; always@(a or g1 or g2 or g3) // 电平触发方式 begin if(g1==0) y=8‘b11111111; // 如果 g1 为 为 0 ,则 y 输出为 11111111 else if(g2==1) y=8‘b11111111; // 如果 g2 为 为 1 ,则 y 输出为 11111111 else if(g3==1) y=8‘b11111111; // 如果 g3 为 为 1 ,则 y 输出为 11111111 else case(a[2:0]) // 判断 a 的值,并通过 a 的值来给 y // 设置输出值 3‘b000:y[7:0]=8‘b11111110; 3‘b001:y[7:0]=8‘b11111101; 3‘b010:y[7:0]=8‘b11111011; 3‘b011:y[7:0]=8‘b11110111; 3‘b100:y[7:0]=8‘b11101111; 3‘b101:y[7:0]=8‘b11011111; 3‘b110:y[7:0]=8‘b10111111; 3‘b111:y[7:0]=8‘b11111111; endcase end endmodule

标签:

原文地址:http://www.cnblogs.com/Fun-with-FPGA/p/4709369.html